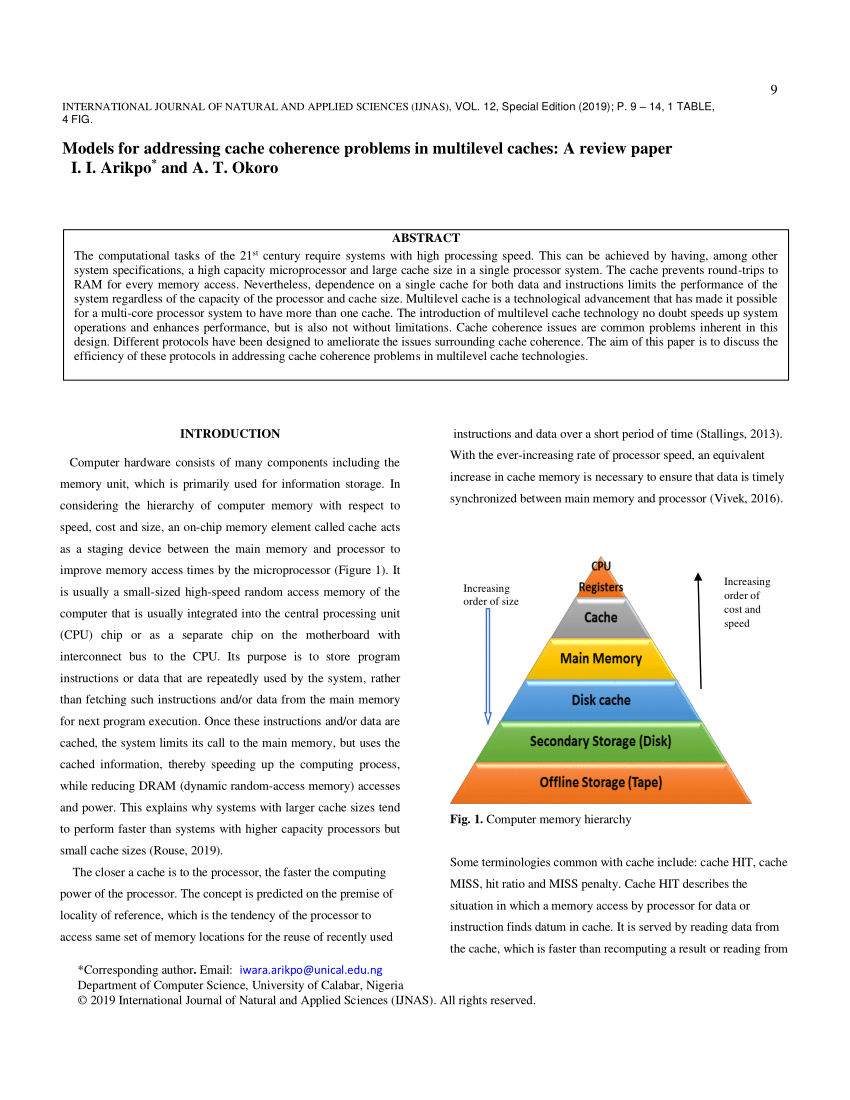

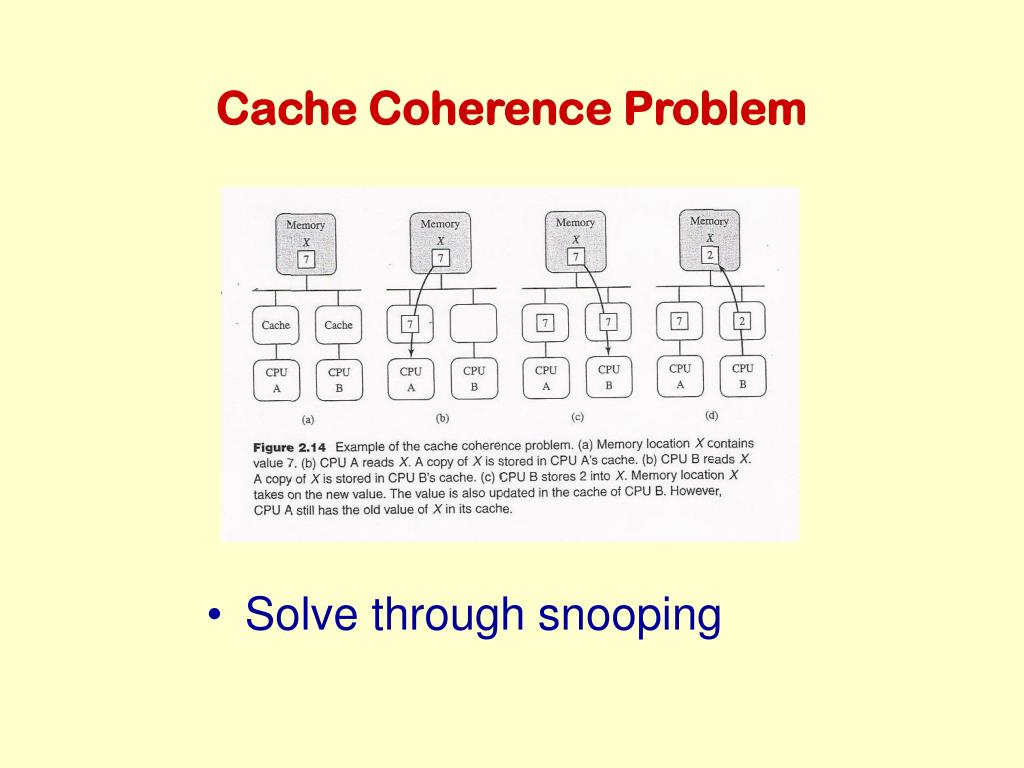

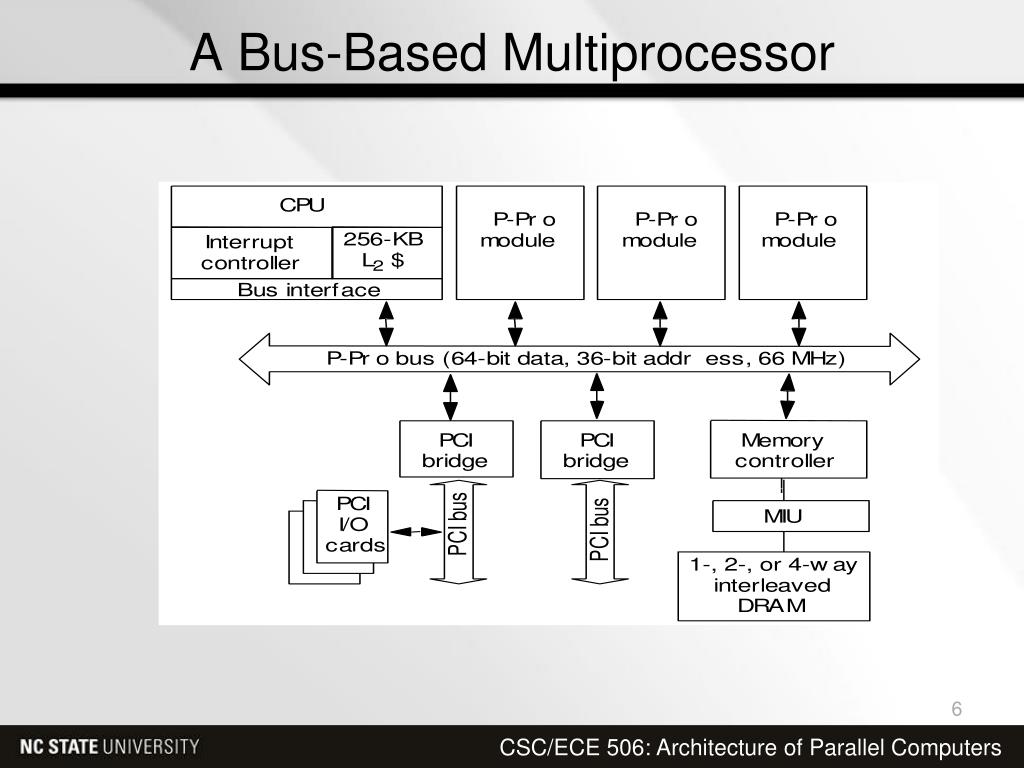

You get the idea.Ĭaches are organized into “lines”, corresponding to aligned blocks of either 32 (older ARMs, 90s/early 2000s x86s/PowerPCs), 64 (newer ARMs and x86s) or 128 (newer Power ISA machines) bytes of memory. At this point, there’s generally more cache levels involved this means the L1 cache doesn’t talk to memory directly anymore, it talks to a L2 cache – which in turns talks to memory. And about 20 years ago, the L1 caches would indeed talk to memory directly. The CPU core’s load/store (and instruction fetch) units normally can’t even access memory directly – it’s physically impossible the necessary wires don’t exist! Instead, they talk to their L1 caches which are supposed to handle it. In modern CPUs (almost) all memory accesses go through the cache hierarchy there are some exceptions for memory-mapped IO and write-combined memory that bypass at least parts of this process, but both of these are corner cases (in the sense that the vast majority of user-mode code will never see either), so I’ll ignore them in this post. (If you are, feel free to skip this section.) I’m assuming you know the basic concept, but you might not be familiar with some of the details. This is a whirlwhind primer on CPU caches. I started writing a first post but quickly realized that there are a few basics I need to cover first. When a processors wishes to update a shared line, the word to be updated is distributed to all others, and caches containing that line can update it.I’m planning to write a bit about data organization for multi-core scenarios. With a write update protocol, there can be multiple writers as well as multiple readers.Once the line is exclusive, the owning processor can make local writes until some other processor requires the same line. When one of the caches wants to perform a write to the line it first issues a notice that invalidates that tine in the other caches, making the line exclusive to the writing cache.Initially, a line may be shared among several caches for reading purposes.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed